Project Description

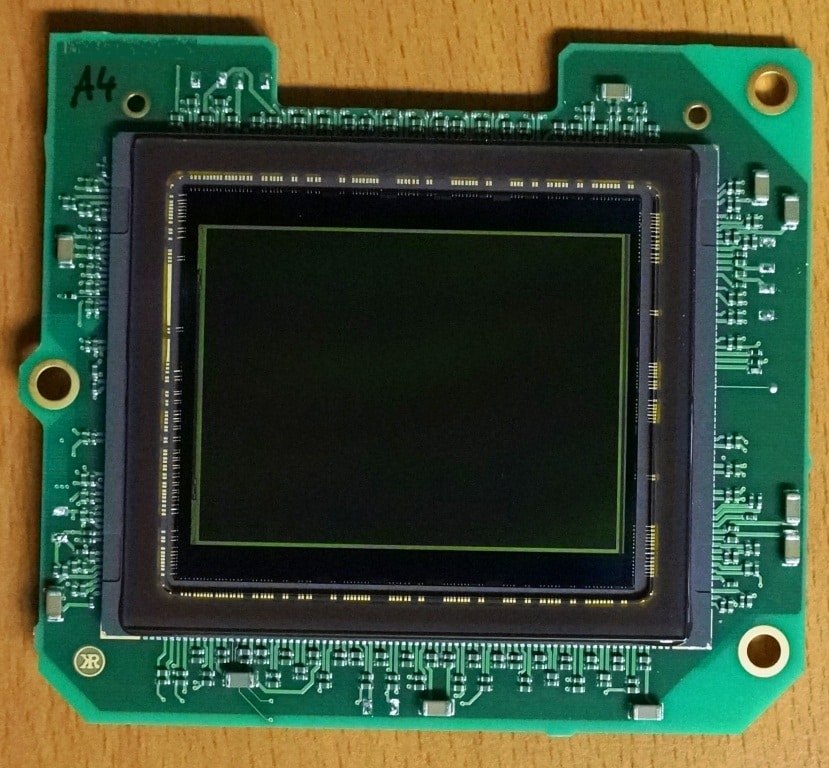

50MP EVALUATION PCB FRONT

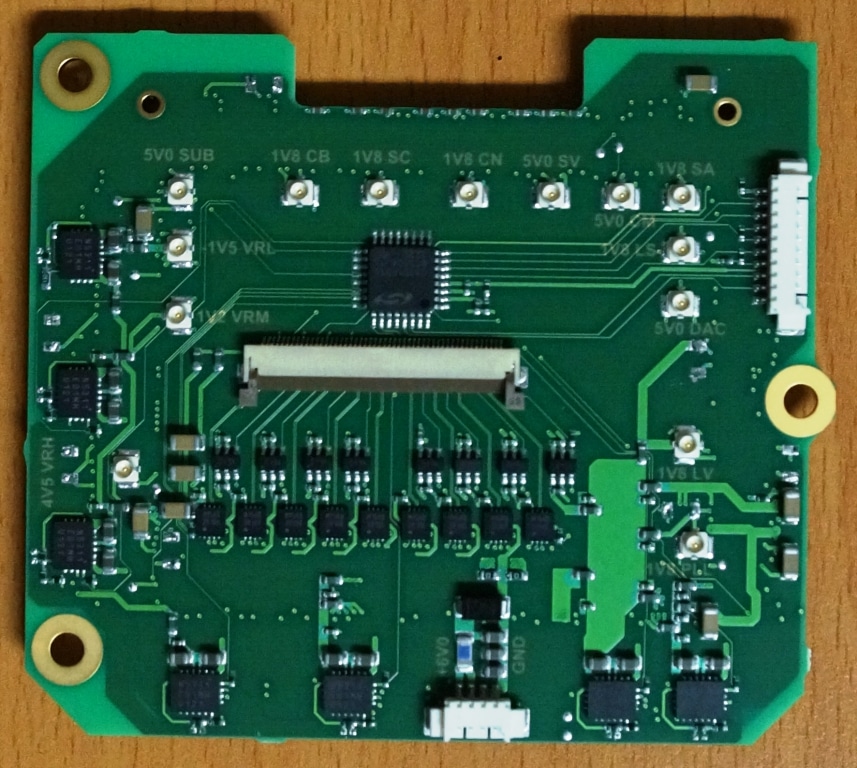

50MP EVALUATION PCB BACK

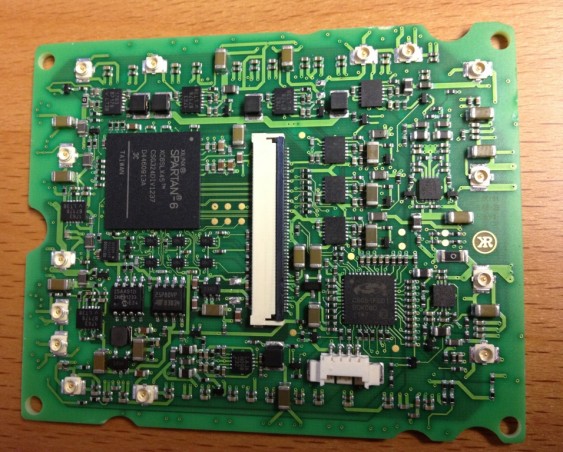

50MP EVALUATION PCB BACK PLATFORM INTEGRATED

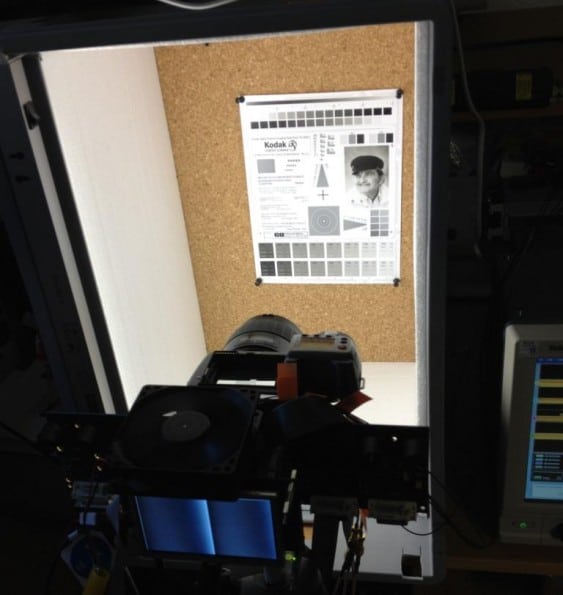

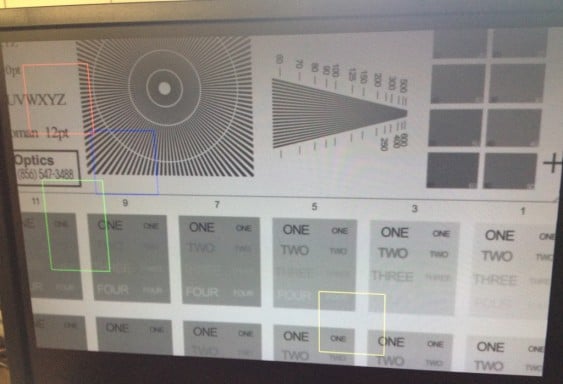

TEST PATTERN IN USE

REGION OF INTEREST SELECTIONS

Task:

To design a platform that allows the evaluation of the optical and electrical characteristics of a mid- format 50 Megapixel CMOS image sensor.

Challenges:

-The sensor has many power rails with strict sequencing and low noise requirements.

– It generates in excess of 300 Megabytes of data per second.

– It is very sensitive to ESD and needs adequate protection in order to survive the handling that is expected to take place in varying test settings.

Solution:

A custom PCB with careful consideration of layer stack arrangement and low noise, fast DC/DC converters provides the foundation of the test bed. An array of u.FL connectors ensures secure access to the key points of interest for noise measurement of the supply rails.

An FPGA module was used to decode the sensors LVDS stream and to perform a simple de-bayer, and pixel sub-sampling for image pre-view. Since the FPGA module had a port for a Tektronix TLA logic- analyzer platform with deep memory acquisition, multiple 50MP frames could be captured and analyzed. The ability to trigger the DPO from the Logic analyzer or a trigger from the FPGA (line select for example), time correlated measurements in the analog and digital domain could be performed. It was therefore possible to identify specific image content or processes in the CMOS sensor as the source of a particular analog noise pattern on the supply rails.

In addition to test equipment aided measurements, we implemented several measurement modules as cores in the FPGA. Regions of interest can be selected by “dialing” color coded frames to the desired part of the image. Measurements such as min & max value, noise floor,histogram etc can be applied to the full image frame or reduced areas of interest.

Technologies used:

Layout know-how, Low noise power POL design, Spartan 6 FPGA, Advanced test equipment (TEK TLA7012 + deep memory acquisition + TEK DPO7035 40Gs 3.5GHz Scope), custom VHDL coding